# Analysis of Interconnection Delay on Very High-Speed LSI/VLSI Chips Using an MIS Microstrip Line Model

HIDEKI HASEGAWA, MEMBER, IEEE, AND SHOUHEI SEKI

**Abstract**—Using an MIS (metal-insulator-semiconductor) microstrip-line model for interconnection and its equivalent circuit representation, on-chip interconnection delay in very high-speed LSI/VLSI's is analyzed in the time domain, changing interconnection geometry, substrate resistivity, and terminal conditions. The results show the following: 1) the “lumped capacitance” approximation is inapplicable for interconnections in very high-speed LSI/VLSI's ( $t_{pd}$  of below 100–200 ps); 2) as compared to the semi-insulating substrate, the presence of the slow-wave mode and mode transition in the semiconducting substrates causes 1.5–2 times increase in the delay time and 2–10 times increase in the rise time; and 3) in order to realize propagation delay times of less than 100 ps per gate at LSI/VLSI levels, the effective signal source resistance of the gate should be less than 500  $\Omega$  so as to long interconnections.

## I. INTRODUCTION

DEVELOPMENT of very high-speed integrated circuits is currently of great technological interest, owing to an ever increasing demand for higher speeds in the areas of high-speed computation, signal processing, data links, and related instrumentation. Indeed, LSI/VLSI's with an average propagation delay per gate  $t_{pd}$  of 100 ps or below will have a great technological impact on these areas, judging from the speed performance of currently available integrated circuits. In the small- to medium-scale integration levels, propagation delay times in the 10–30-ps range have already been realized with GaAs MESFET, HEMT, Josephson Junction, and Si NMOS technologies. If such speeds are to be realized in LSI/VLSI integration levels, however, on-chip interconnection delay and crosstalk are expected to become important problems due to the increased length of interconnections. Proper design considerations to minimize them should be paid in order to take full advantage of the inherent speed capability of the device.

The purpose of the present paper is to investigate the on-chip interconnection delay in very high-speed integrated circuits, using an MIS (metal–insulator–semiconductor) microstrip line model. Effects of interconnection geometry, substrate conductivity, and device driving capability on propagation delay, distortion, and multiple reflection are analyzed. The problem of crosstalk due to interconnection is analyzed in a separate paper [1], using a coupled multi-conductor MIS stripline model.

The result of this paper shows that the conventional “lumped capacitance” approximation for interconnections is no longer adequate for the design of LSI/VLSI's with  $t_{pd}$  of below 100 ps; therefore, the interconnections should be treated as miniaturized microwave networks. In the semiconducting substrate, wave propagation is dispersive due to slow-wave mode propagation and mode transition. Owing to this, propagation delay and rise times of high-speed pulses are deteriorated in the semiconducting substrate as compared with the semi-insulating substrate. It is also shown that the driving capability of the device to drive long interconnections is essentially important for realization of very high-speed LSI/VLSI's.

## II. MODEL AND METHOD OF ANALYSIS

### A. Length of Interconnections in LSI/VLSI's

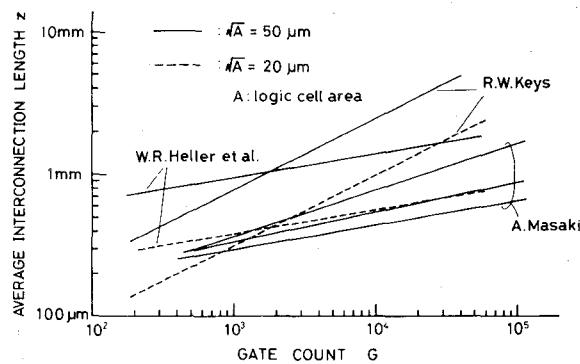

The average interconnection length  $L$  per gate on LSI/VLSI chips is known to increase with the gate count  $G$ , as in the following empirical formula:

$$L = KG^\alpha \sqrt{A} \quad (1)$$

where  $K$  and  $\alpha$  are empirical constants, and  $A$  is the logic cell layout area. Equation (1) can also be derived theoretically [2], [3] on the basis of the Rent's rule [4] concerning the pin versus gate count relationship. Using the reported values of  $K$  and  $\alpha$  [3], [5], [6], the average interconnection length is plotted versus gate count in Fig. 1. As seen in Fig. 1, the average interconnection length becomes 0.5–5 mm for  $G = 10^3$ – $10^4$ . Thus, speed is limited not only by the device speed itself, but by the fact that each gate should drive interconnections at a high speed. Previously, this effect has been treated in terms of the “lumped capacitance” of interconnections [6]–[10]. However, since the propagation time of an ideal TEM wave over 1-mm distance is typically 8–10 ps on a semiconductor substrate ( $\epsilon_r = 12$ –13), validity of such an approach becomes very doubtful in high-speed LSI/VLSI's. Thus, the transmission-line effects of interconnections have to be investigated.

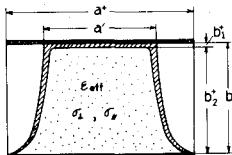

### B. An MIS Microstrip Line Model and Approach for Analysis

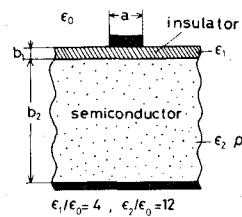

An MIS-type single microstrip line model shown in Fig. 2 is used for the analysis. It is a microstrip line formed on a surface passivated semiconductor substrate with a metal-

Manuscript received May 30, 1984.

The authors are with the Department of Electrical Engineering, Faculty of Engineering, Hokkaido University, Sapporo, 060 Japan.

Fig. 1. The average interconnection length plotted versus gate count  $G$ .  $A$  is the logic cell area.

Fig. 2. An MIS (metal-insulator-semiconductor) microstrip line model for interconnection.

lized back. In practice, a metallized back is not necessarily formed. However, when the chip is mounted, an equivalent situation is usually brought about.

Owing to the finite conductivity of the semiconductor substrate, a rigorous analysis of wave propagation along such a stripline is difficult, and can be done only numerically in the frequency domain, using the spectral-domain method [11], [12], mode-matching method [12], or by the finite-element method [13]. But these complicated numerical procedures require large computational resources and are generally time consuming. Additionally, they tend to run into difficulties of divergence from the true solution if the initialization is inappropriate [13]. Thus, they do not seem to be practical for a quick estimate of on-chip delay in the time domain, changing the parameters over wide ranges.

The equivalent circuit approach by Hasegawa *et al.* [14]–[16], which allows a closed-form analysis in the frequency domains, is employed here as the basis for the time-domain analysis. In this approach, the fundamental TM mode of an MIS parallel plate waveguide is rigorously analyzed [13], [17], and an equivalent circuit representation for an MIS microstrip line is set up on the basis of physical understanding of the modes. Then, each equivalent circuit parameter is evaluated to take account of the fringing effect of the microstrip of the finite width.

### C. Propagation Modes

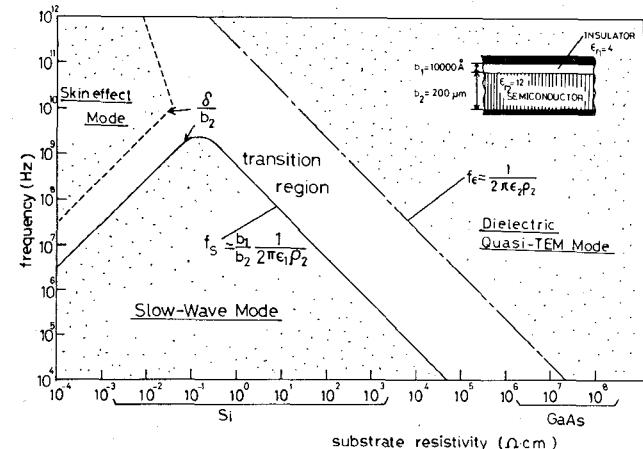

The resistivity-frequency mode chart of the MIS microstrip line based on such an analysis is schematically shown in Fig. 3. When the substrate conductivity is low, the substrate acts like an insulator, and the dielectric quasi-TEM mode propagates. When the substrate conductivity is high, the substrate acts like an imperfect metal wall with a

Fig. 3. Resistivity-frequency mode chart of the MIS microstrip line.  $\delta$  is the skin depth in semiconductor, and  $\rho$  is the semiconductor resistivity.

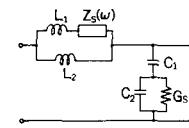

Fig. 4. Equivalent circuit per unit length of the MIS microstrip line.

large skin effect, resulting in a skin-effect mode. A remarkable point concerning the MIS waveguide is that the slow-wave mode propagates when the substrate is semiconducting and the frequency is low. In the low-frequency limit, electric-field lines do not penetrate into the semiconductor, whereas the magnetic-field lines can fully penetrate into it. This results in spatially separated storage of electric and magnetic energies, leading to propagation of the slow-wave mode. It should be noted that the slow-wave mode region extends into the gigahertz range at a certain resistivity. Propagation of such a mode was experimentally confirmed by Hasegawa *et al.* [13], [18], and several authors have investigated its application to variable delay lines [19]–[21]. Its application to wavelength reduction in GaAs MMIC's using an MIS coplanar stripline was proposed [22] and analyzed [12]. It will be shown here that the slow-wave mode and the related mode transition have large effects on the fast-pulse transmission on semiconductor chips.

### D. Equivalent Circuit Representation

The equivalent circuit representation per unit length of the MIS microstrip line used in this study is shown in Fig. 4. The representation is slightly modified from the original one in [13] to take account of the mode transition more appropriately. In Fig. 4,  $C_1$  is the insulator capacitance,  $C_2$  and  $G_s$  are the capacitance and transverse conductance of the semiconductor.  $L_1$  is the inductance of the insulator,  $L_2$  is the inductance of the air region, and  $Z_s(\omega)$  is the impedance of the semiconductor region, including the semiconductor inductance and longitudinal resistance. Due to the skin effect in the semiconductor, the semiconductor impedance is frequency dependent. The derivation of the explicit formulas for the circuit elements in the equivalent circuits is summarized in the Appendix. In particular, an

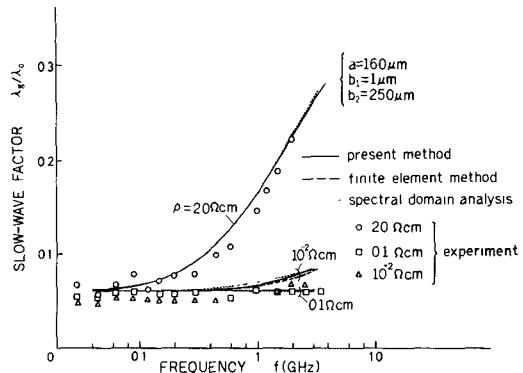

Fig. 5. Plots of the slow-wave factor as obtained by the present and other theories [11], [13] together with experimental data [14]. In the case of  $\rho = 0.1 \Omega \cdot \text{cm}$  and  $\rho = 20 \Omega \cdot \text{cm}$ , the agreement between the present results and those by the finite-element method is extremely good; therefore, one curve representing two sets of results was drawn in the figure.

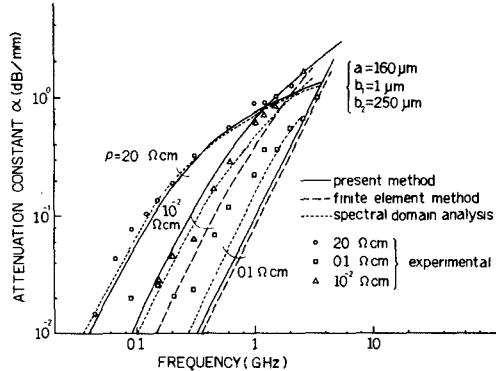

Fig. 6. Plots of the attenuation constant as obtained by the present and other theories [11], [13] together with experimental data [14]. Present results are again in good agreement with the finite-element method in the case of  $\rho = 20 \Omega \cdot \text{cm}$ , where two curves merged together.

analytic expression for  $Z_s(\omega)$  is newly derived in order to improve the accuracy in treating the skin-effect loss under the finite width microstrip more accurately than our previous analyses [14]–[16] and the analysis by Hughes and White [17].

#### E. Results of Frequency-Domain Analysis

In order to check the validity of the present approach, transfer characteristics in the frequency domain, calculated using the equivalent circuit shown in Fig. 4, are compared with the results of the numerical analyses [11], [13] and with our previous experimental data [14]. Plots of the slow-wave factor and the attenuation constant are shown in Figs. 5 and 6, respectively. Agreement is very good, particularly for the practically important resistivity range of above  $10^{-1} \Omega \cdot \text{cm}$ . The experimentally observed attenuation constant is found to be somewhat higher than theoretical values, and this is presumably due to the metallic loss which is not considered in the present theory. The good agreement obtained here seems to indicate that the present method may be useful not only to pulse transmission calculation but also to analysis and design of MIS transmission lines for microwave analog applications.

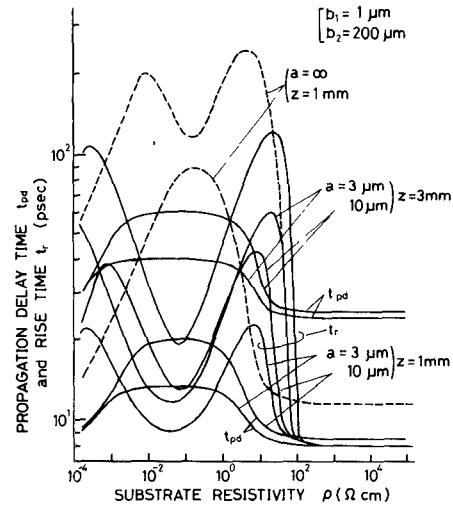

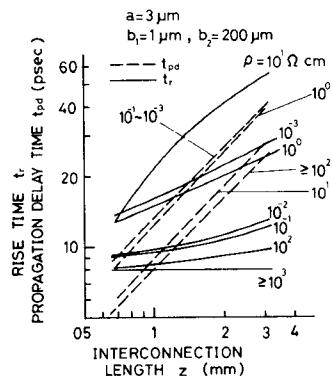

Fig. 7. Calculated propagation delay time and rise time of the step response for a semi-infinite interconnection (or matched termination). The rise time of the input pulse is assumed to be 8 ps.

### III. TIME-DOMAIN RESULTS AND DISCUSSION

#### A. Procedure for Transient Calculation

Calculation of the transient waveforms were done in the following way. Given an interconnection geometry, the equivalent circuit parameters were computed. By substituting these values into the analytic expressions for the characteristic impedance and propagation constants based on the equivalent circuit in Fig. 4, transient waveforms under arbitrary excitation and termination conditions can be calculated by the inverse Laplace transform. The inverse Laplace transform was carried out numerically using the standard trigonometric function expansion method.

#### B. Matched Termination

Fig. 7 shows the calculated delay time (time to 50-percent rise) and rise time (time between 10–90-percent rise) of the step response as a function of the semiconductor substrate resistivity. The response is calculated at positions with distance of  $z = 1$  and 3 mm from the signal source. The interconnection length is assumed to be semi-infinite or the line is assumed to be terminated with a hypothetical matched load. The behavior of the delay and rise times versus substrate resistivity can be explained in terms of the three fundamental modes, i.e., the dielectric quasi-TEM mode, slow-wave mode, and skin-effect mode. An increase of the delay time at the mid-resistivity range is due to the slow-wave mode, and rise-time peaks on both sides of the delay time-peak are due to the mode transition from the slow-mode either to the dielectric quasi-TEM mode or to the skin-effect mode. It should be noted that considerable deterioration of the pulse response takes place at resistivities of  $1$ – $100 \Omega \cdot \text{cm}$ , which are frequently used in Si technology. The basic reason for this deterioration of rise time associated with the transition from the slow-wave mode to the dielectric quasi-TEM mode is that the element  $G_s$  in Fig. 4 dominates for most of the frequency components involved, and the line behaves like an LG line.

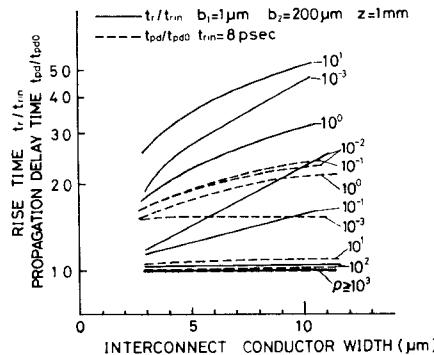

Fig. 8. Dependence of delay time and rise time on the interconnection strip width for a semi-infinite interconnection (or matched termination). The rise time of the input pulse is assumed to be 8 ps.

Fig. 9. Dependence of delay time and rise time on the distance  $z$  from the signal source on a semi-infinite interconnection (matched termination). The rise time of the input pulse is assumed to be 8 ps.

Therefore, the wave propagation proceeds more or less like diffusion, resulting in a slow buildup of the pulse waveform.

The dependences of the delay time and rise time on the strip width are plotted in Fig. 8. Fig. 9 shows the dependences of the delay and rise time on the distance  $z$ . Rise-time deterioration near  $10 \Omega \cdot \text{cm}$  is almost proportional to line length, and this reflects the above-mentioned diffusion-like nature of wave propagation.

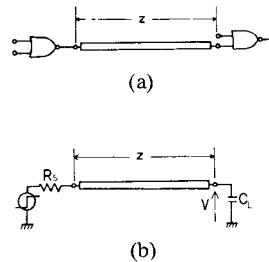

### C. Interconnections Between Logic Gates and Transient Waveforms

The present model was further applied to the situation where two logic gates are connected by an interconnection as shown in Fig. 10(a). For the calculation, the logic gate output was represented by its effective signal source resistance  $R_s$ , and the gate input was represented by an input capacitance  $C_L$  as shown in Fig. 10(b). It can be shown that, in the gates consisting of FET-type devices such as MOSFET's, MESFET's, and HEMT's,  $R_s$  is approximately equal to the inverse of the transconductance  $g_m$  of the switching or load transistor depending on which is taking part in the transient. As for the input capacitance, a standard 1-μm-gate GaAs MESFET has approximately a gate capacitance of 1 fF per 1-μm gatewidth.

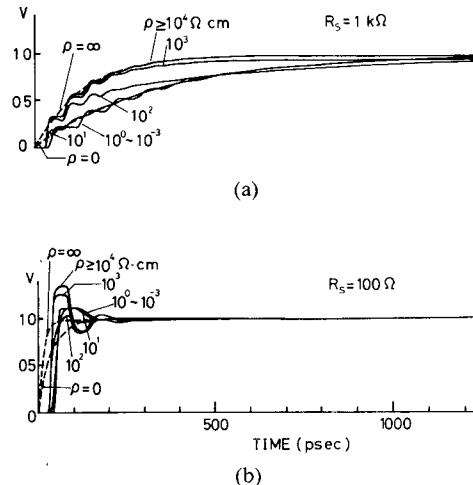

Examples of the calculated transient waveforms of step response are shown in Fig. 11 (a) and (b). The 3-μm rule is

Fig. 10. (a) Interconnection between two logic gates and (b) its model.  $R_s$  is the effective signal source resistance of the first gate and  $C_L$  is the input capacitance of the second gate.

Fig. 11. Examples of step response waveform. (a)  $R_s = 1 \text{ k}\Omega$  and (b)  $R_s = 100 \Omega$ .  $a = 3 \mu\text{m}$ ,  $z = 3 \text{ mm}$ ,  $b_1 = 1 \mu\text{m}$ ,  $b_2 = 200 \mu\text{m}$ .

assumed, and the interconnection length  $z$  is taken to be 3 mm. Dashed curves are the waveforms based on the "lumped capacitance" approximation for the interconnection, where two different capacitance values are used. One is based on the assumption that the semiconductor substrate can be regarded as the perfect insulator ( $\rho = \infty$ ), and the other is on the assumption that it can be regarded as a perfect conductor ( $\rho = 0$ ). It is seen that the "lumped capacitance" approximation is reasonably good, when the signal source impedance  $R_s$  is high and the response is slow. But, when  $R_s$  is low and a high-speed response is realized, the "lumped capacitance" approximation becomes excessively inadequate.

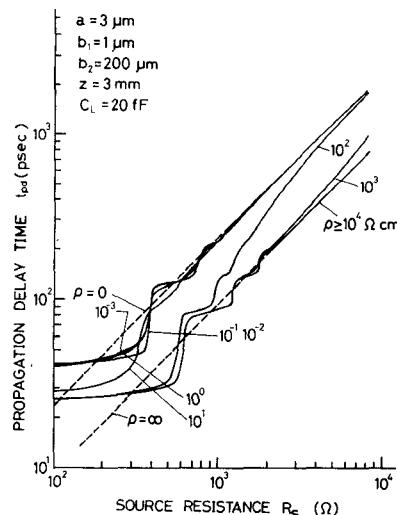

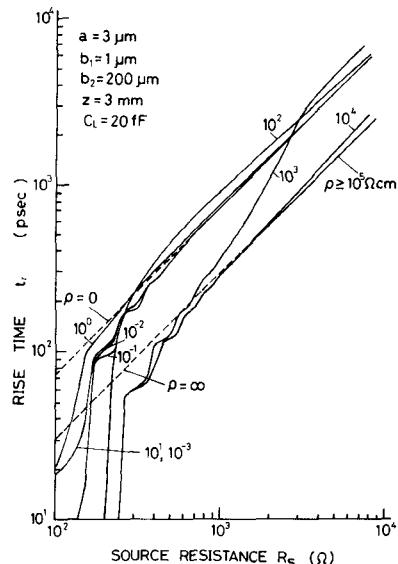

### D. Effects of Substrate Resistivity and Device Transconductance

The calculated propagation delay time  $t_{pd}$  (delay up to 50-percent rise) and rise time (10–90-percent rise) as observed at the input of the second gate are summarized in Figs. 12 and 13, respectively. Those values, as obtained by the aforementioned two limiting cases of "lumped capacitance" approximation, are also shown by the dashed lines. It is more clearly seen in Figs. 12 and 13 that the "lumped capacitance" approximation is valid only in LSI/VLSI's with  $t_{pd}$  above 100–200 ps. In Fig. 12, the rise time is seen to become higher for large values of  $R_s$  and higher values of substrate resistivity than the upper dashed curve corre-

Fig. 12. Calculated delay time versus signal source impedance of gate  $R_s$ .

Fig. 13. Calculated rise time versus signal source impedance of gate  $R_s$ .

sponding to the "lumped capacitance" approximation with an insulator approximation for the substrate ( $\rho = \infty$ ). This may appear physically unacceptable because the lumped capacitance approximation is expected to be valid in this region. However, it actually reflects the Maxwell-Wagner-type interfacial charge relaxation effect, and can be explained by including the "lumped conductance" of the substrate.

The results in Figs. 12 and 13 strongly indicate that semi-insulating substrates offer a significant advantage over semiconducting substrates in both delay and rise times. Particularly, rise-time deterioration due to mode transition from the slow-wave mode to the dielectric quasi-TEM mode, as explained previously, is very severe in the substrate resistivity range of  $10^0$ – $10^1$   $\Omega \cdot \text{cm}$ , requiring low source resistance  $R_s$  of 120–200  $\Omega$  to achieve  $t_r$  of below 100 ps. It should be noted that the above substrate resistivity range is actually employed in the current silicon technology. A factor of a 1.5–2 increase in delay is also caused

TABLE I

TRANSCONDUCTANCE  $g_m$  AND  $R_s$  OF VARIOUS FET DEVICES

(gate length = 1  $\mu\text{m}$ ; gate width = 10  $\mu\text{m}$ )

| DEVICE      | $g_m$ (mS) | $R_s$ ( $\Omega$ ) |

|-------------|------------|--------------------|

| GaAs MESFET | 1.4        | 710                |

| Si MOSFET   | 0.8        | 1250               |

| HEMT (77K)  | 2.9        | 350                |

Note: The data are converted from [24]. For comparison, a Si bipolar device with a  $1 \times 2\text{-}\mu\text{m}$  emitter size expected to have a  $g_m$  of 19.2 mS [24]. An AlGaAs/GaAs heterojunction bipolar transistor with a  $4.5 \times 10\text{-}\mu\text{m}$  emitter size exhibited a transconductance of 47.5 mS [25].

by the slow-wave mode, if the resistivity is below  $1 \Omega \cdot \text{cm}$ . Up to now, such effects have not been reported experimentally in Si IC's, but this is simply because the speed performance is still not fast enough to see them.

Another very important conclusion which can be drawn from Figs. 12 and 13 is that the strong driving capability of the device is essential in realizing very high-speed LSI/VLSI's. Table I summarizes typical values of the transconductance  $g_m$  and corresponding values of  $R_s$  for various switching devices (1- $\mu\text{m}$  feature size) taken from the literature [24], [25]. It should be noted that in the conventional E/D or E/R gate configuration,  $R_s$  of the load devices should at least be 4–5 times of that of the switching device, and therefore the transient involving the load device limits the speed. It can be said that the driving capability of the currently available device is barely sufficient to realize LSI/VLSI's with  $t_{pd}$  of below 100 ps. HBT and HEMT technologies seem promising in this respect for future improvement. Since (1), for the interconnection length, more or less assumes a random logic configuration (such as gate arrays), an alternative approach to fully exploit the inherent speed advantage of the devices is to improve the chip architecture so as to avoid long interconnections.

#### IV. CONCLUSION

On-chip interconnection delay in very high-speed LSI/VLSI's is analyzed, using a MIS microstrip line model and its equivalent circuit representation which allows closed-form formulas in the frequency domain. The main conclusions of the present study are the following.

1) The lumped capacitance approximation of interconnections cannot be used in LSI/VLSI's with  $t_{pd}$  below 100–200 ps. Microwave considerations are required in the logic, circuit, and layout design of such very high-speed integrated circuits.

2) To drive interconnections at high speeds, the driving capability of the device per unit layout area is essentially important. Effective signal source resistance of the gate should be less than 500  $\Omega$  to achieve the propagation delay time of less than 100 ps in LSI/VLSI's on semi-insulating substrates where the average interconnection length is 1–3 mm.

Fig. 14. The inhomogeneous parallel waveguide mapped from the MIS microstrip line by Schwarz-Christoffel transformation.

3) The semi-insulating property of substrates offers a factor of 1.5–2 advantage in propagation delay time with a much steeper rise time for high-speed pulse transmission in LSI/VLSI's because of absence of the slow-wave mode and mode transition that are present in semiconducting substrates. To achieve the same speeds, semiconducting substrates require devices with larger driving capability.

#### APPENDIX DETERMINATION OF EQUIVALENT CIRCUIT PARAMETERS

In the quasi-static limit, fields are determined by the Laplace equation. An unloaded single microstrip line with strip width  $a$  and height  $b = b_1 + b_2$  can be transformed to a parallel-plate waveguide by the following Schwarz-Christoffel (S-C) transformation:

$$W = -j \frac{\pi}{2K} W_1 - j \frac{2K'b}{\pi} Z \left( \frac{\pi W_2}{2b} \right)$$

$$h \equiv \left| \frac{dW}{dW_1} \right| = \left| E' - K'k^2 \operatorname{sn}^2 \frac{\pi W^2}{2b} \right| \quad (A1)$$

where  $h$  is the scaling parameter of the transformation,  $Z$  is Jacobi's Zeta function,  $\operatorname{sn}$  is Jacobi's elliptic function, and  $K'$  and  $E'$  are complete elliptic integrals of the first and second kinds with modulus  $k$ , respectively. Then, the present MIS microstrip line is mapped to the inhomogeneous parallel waveguide shown in Fig. 14 by the same S-C transformation. In terms of the length parameters in Fig. 14, the circuit elements are given by the following formulas:

$$C_1 = \frac{a^+}{b_1^+} = \epsilon_1 \frac{a}{b_1} \quad C_2 = \epsilon_{\text{eff}} \frac{a^+}{b_2^+} \quad G_s = \sigma_{\perp} \frac{a^+}{b_2^+}$$

$$L_1 = \mu_0 \frac{b_1^+}{a'} \quad L_2 = \mu_0 \frac{b_2^+}{a^+ - a'} \quad (A2)$$

where  $\epsilon_{\text{eff}}$  and  $\sigma_{\perp}$  are the effective dielectric constant and effective transverse conductivity reflecting partial filling, which are given in [14]. For the actual calculation of the length parameters, approximate formulas in [14] were used.

In order to include the skin effect more accurately in the evaluation of  $Z_s(\omega)$ , transformation of the Helmholtz equation for  $E_z$  is considered. The Helmholtz equation is generally variant under the S-C transformation. However, it can be regarded approximately invariant in the vicinity of the underneath of the strip, which is physically important for the skin effect under the following conditions. The conditions are that appropriate averaged values are assigned to the scaling parameter  $h$  of the S-C transformation and also to the effective longitudinal conductivity  $\sigma_{\parallel}$

to be used in the transformed domain. This allows us to use the result of the parallel-plate waveguide analysis [14] in the transformed domain for the evaluation of the semiconductor impedance  $Z_s(\omega)$ . The resulting formulas are summarized as follows:

$$Z_s(\omega) = j\omega\mu_0 \left( \frac{b_2^+}{a'} \right) \left( \frac{1}{\gamma_m b_2^+} \right) \tanh \gamma_m b_2^+ \quad (A3)$$

$$\gamma_m = \sqrt{j\omega\mu_0\sigma_{11}}$$

$$\sigma_{\parallel} = \sigma \bar{h}^2$$

$$\bar{h} = \sqrt{|E'(E' - K'k^2)|}$$

where  $\bar{h}$  is the average scaling parameter between the center of the top plane and the center of the bottom plane in Fig. 14.

#### ACKNOWLEDGMENT

The authors would like to express their sincere thanks to Dr. H. Ohno, Hokkaido University, and Dr. A. Masaki, Hitachi Central Research Laboratory, for their useful discussions and comments.

#### REFERENCES

- [1] S. Seki and H. Hasegawa, "Analysis of crosstalk in very high-speed LSI/VLSIs using a coupled multi-conductor stripline model," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 1715–1720, Dec. 1984.

- [2] W. E. Donath, "Placement and average interconnection lengths of computer logic," *IEEE Trans. Circuits Syst.*, vol. CAS-26, pp. 272–277, Apr. 1979.

- [3] A. Masaki, "On the performance improvement of LSIs for computer logic," Ph.D. dissertation, Dept. of Electron. Eng., University of Tokyo, 1982 (in Japanese, unpublished).

- [4] E. S. Landman and R. L. Russo, "On a pin versus block relationships for partitions of logic graphs," *IEEE Trans. Comput.*, vol. C-20, pp. 1469–1479, Dec. 1971.

- [5] W. R. Heller, W. F. Mikhail, and W. E. Donath, "Prediction of wiring space requirements for LSI," in *Proc. 14th Design Automation Conf.* (New Orleans, LA), June 20–22, 1977, pp. 32–34.

- [6] R. W. Keyes, "The evolution of digital electronics towards VLSI," *IEEE Trans. Electron Devices*, vol. ED-26, pp. 271–279, Apr. 1979.

- [7] A. K. Sinha, J. A. Cooper, and H. J. Levinstein, "Speed limitations due to interconnect time constants in VLSI integrated circuits," *IEEE Electron Device Lett.*, vol. EDL-3, pp. 90–92, Apr. 1982.

- [8] C. P. Yuan and T. N. Trick, "A simple formula for the estimation of the capacitance of two-dimensional interconnects in VLSI circuits," *IEEE Electron Device Lett.*, vol. EDL-3, pp. 391–393, Dec. 1982.

- [9] H-T. Yuan, Y-T. Ling, and S-Y. Chiang, "Properties of interconnection of silicon, sapphire and semi-insulating gallium arsenide substrates," *IEEE Trans. Electron Devices*, vol. ED-29, pp. 639–644, Apr. 1982.

- [10] A. Masaki and T. Chiba, "Design aspects of VLSI for computer logic," *IEEE Trans. Electron Devices*, vol. ED-29, pp. 751–756, Apr. 1982.

- [11] P. Kennis and L. Faucon, "Rigorous analysis of planar MIS transmission lines," *Electron. Lett.*, vol. 17, no. 13, pp. 454–456, June 1981.

- [12] Y. Fukuoka, Y-C. Chi, and T. Itoh, "Analysis of slow-wave coplanar waveguide for monolithic integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 567–573, July 1983.

- [13] M. Aubourg, J-P. Villotte, F. Godon, and Y. Garaut, "Finite element analysis of lossy waveguides—Application to microstrip lines on semiconductor substrates," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-31, pp. 326–330, Apr. 1983.

- [14] H. Hasegawa, M. Furukawa, and H. Yanai, "Properties of microstriplines on Si-SiO<sub>2</sub> system," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-19, pp. 869–881, Nov. 1971.

- [15] H. Hasegawa, N. Tetsutani, and T. Sawada, "Transmission properties of microstrip and coplanar striplines for GaAs digital and analog integrated circuits," presented at the IEEE GaAs IC Symp., Las Vegas, NV, Nov. 4-6, 1980.

- [16] S. Seki and H. Hasegawa, "Pico-second pulse response of interconnections of high-speed GaAs and Si LSIs," in *Tech. Dig. 1982 GaAs IC Symp.*, (New Orleans, LA), Nov. 9-11, 1982.

- [17] H. Guckel, P. A. Brennan, and I. Palocz, "A parallel waveguide approach to miniaturized planar transmission lines for integrated circuits," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-15, pp. 468-476, Aug. 1967.

- [18] H. Hasegawa, M. Furukawa, and H. Yanai, "Slow wave propagation along a microstrip line on Si-SiO<sub>2</sub> system," *Proc. IEEE*, vol. 59, pp. 869-881, Feb. 1971.

- [19] J. M. Jaffe, "A high-frequency variable delay line," *IEEE Trans. Electron Devices*, vol. ED-19, pp. 1292-1294, 1972.

- [20] G. W. Hughes and R. M. White, "MIS and Schottky barrier microstrip devices," *Proc. IEEE*, vol. 60, pp. 1460-1461, 1972.

- [21] D. Jager, "Slow-wave propagation along variable Schottky-contact microstrip line," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-24, pp. 566-573, 1976.

- [22] H. Hasegawa and H. Okizaki, "M.I.S. and Schottky slow-wave coplanar striplines on GaAs substrates," *Electron. Lett.*, vol. 13, pp. 663-664, Oct. 1977.

- [23] G. W. Hughes and R. M. White, "Microwave properties of nonlinear MIS and Schottky-barrier microstrip," *IEEE Trans. Electron Devices*, vol. ED-22, pp. 945-956, Oct. 1975.

- [24] P. M. Solomon, "A comparison of semiconductor devices for high-speed logic," *Proc. IEEE*, vol. 70, pp., May 1982.

- [25] T. Sugita, H. Ito, and T. Ishibashi, "AlGaAs/GaAs heterojunction bipolar transistors with cutoff frequencies above 25 GHz," presented at IEEE 42nd Annual Device Research Conf., paper VA-1, June 1984.

+

**Hideki Hasegawa** was born in Tokyo, Japan, on June 22, 1941. He received the B.S., M.S., and Ph.D. degrees in electronic engineering from

the University of Tokyo, Tokyo, Japan, in 1964, 1966, and 1970, respectively.

In 1970, he joined the faculty of the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan, as a Lecturer. In 1971, he became an Associate Professor and, in 1980, a Professor, both in the same department. From 1973 to 1974, he was on sabbatical leave at the Department of Electrical and Electronic Engineering, the University of Newcastle-upon-Tyne, England, as a Visiting Research Fellow.

His current research interests include MBE and OM VPE growth, characterization, and processing of III-V compound semiconductors, surface and interface properties of compound semiconductors, high-speed logic, and microwave and O/E IC's using GaAs, InP, and related compounds. He is also interested in growth, characterization, and device applications of a-Si films.

Dr. Hasegawa is a member of the Institute of Electronics and Communication Engineers of Japan, the Japan Society of Applied Physics, the Institute of Electrical Engineers of Japan, and the Japan Association of Crystal Growth.

+

**Shouhei Seki** was born in Hokkaido, Japan, on November 16, 1956. He received the B.S. and M.S. degrees in electrical engineering from Hokkaido University, Sapporo, Japan, in 1980, and 1982, respectively. He is working towards the Ph.D. degree in the same department.

His research interests include design and analysis of very high-speed integrated circuits and microwave IC's.

Mr. Seki is a member of the Institute of Electronics and Communication Engineers of Japan, and the Japan Society of Applied Physics.